# **Composition and Refinement of Discrete Real-Time Systems**

Jonathan S. Ostroff<sup>1</sup> Department Of Computer Science, York University, 4700 Keele Street, North York Ontario, Canada, M3J 1P3. Email: jonathan@cs.yorku.ca Tel: 416-736-2100 X77882 Fax: 416-736-5872.

**Abstract**: Reactive systems exhibit ongoing, possibly non-terminating, interaction with the environment. Real-time systems are reactive systems that must satisfy quantitative timing constraints. This paper presents a structured compositional design method for discrete real-time systems that can be used to combat the combinatorial explosion of states in the verification of large systems. A *composition rule* describes how the correctness of the system can be determined from the correctness of its modules, without knowledge of their internal structure. The advantage of compositional verification is clear. Each module is both simpler and smaller than the system itself. Composition requires the use of both model-checking and deductive techniques. A *refinement rule* guarantees that specifications of high-level modules are preserved by their implementations. The *StateTime* toolset is used to automate parts of compositional designs using a combination of model-checking and simulation. The design method is illustrated using a reactor shutdown system that cannot be verified using the StateTime toolset (due to the combinatorial explosion of states) without compositional reasoning. The reactor example also illustrates the use of the refinement rule.

**Keywords**: Real-time reactive systems, formal methods tools, statecharts, temporal logic, modules, abstraction, refinement, composition, model checking.

<sup>1.</sup> This research was supported with the help of NSERC (National Science and Engineering Research Council of Canada).

# **Table of Contents**

| 1.0 | Intro       | duction                                     | 3  |

|-----|-------------|---------------------------------------------|----|

| 2.0 | Back        | cground                                     | 6  |

|     | 2.1         | Real Time Temporal Logic (RTTL)             | 6  |

|     | 2.2         | Timed Transition Models (TTMs)              | 8  |

|     | 2.3         | Parallel composition of TTMs                | 12 |

|     | 2.4         | Overview of the StateTime toolset           | 12 |

| 3.0 | Mod         | ules and module composition                 | 15 |

|     | 3.1         | Parallel composition of modules             | 16 |

|     | 3.2         | Modes of interface variables                | 19 |

|     | 3.3         | A small example of compositional reasoning  | 20 |

| 4.0 | Mod         | ule refinement                              | 23 |

|     | 4.1         | Observation equivalence of TTMs             | 23 |

|     | 4.2         | Observation equivalence of modules          | 27 |

| 5.0 | Mod         | ular Design of the delay reactor trip (DRT) |    |

|     | 5.1         | Informal description of the problem         |    |

|     | 5.2         | Formal requirements                         |    |

|     | 5.3         | Problem to be solved                        |    |

|     | 5.4         | Controller design                           |    |

|     | 5.5         | Refining the controller                     |    |

|     | 5.6         | The design method                           |    |

| 6.0 | Cond        | clusions and related work                   |    |

| 7.0 | References4 |                                             | 42 |

# Figure

| FIGURE 1.  | Structure diagram for compositional design method               | 5  |

|------------|-----------------------------------------------------------------|----|

| FIGURE 2.  | Plant module                                                    | 14 |

| FIGURE 3.  | The relay module                                                | 20 |

| FIGURE 4.  | Module for majority voting logic                                | 21 |

| FIGURE 5.  | Observably equivalent TTMs                                      | 24 |

| FIGURE 6.  | Analog implementation of the delay relay trip timing            | 29 |

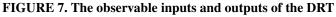

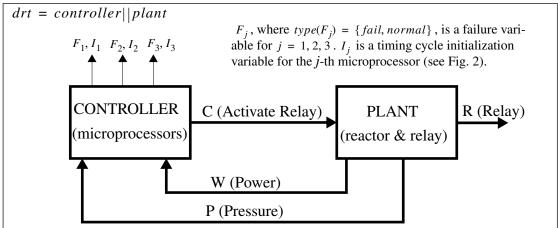

| FIGURE 7.  | The observable inputs and outputs of the DRT                    | 30 |

| FIGURE 8.  | Architecture of the controller based on majority voting control | 32 |

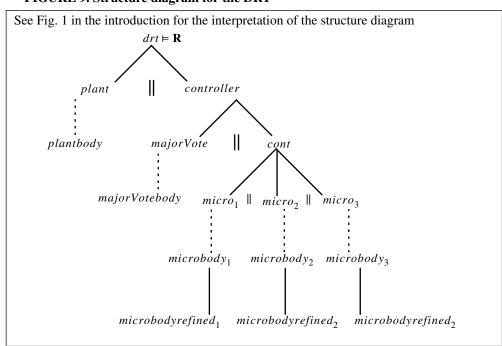

| FIGURE 9.  | Structure diagram for the DRT                                   | 34 |

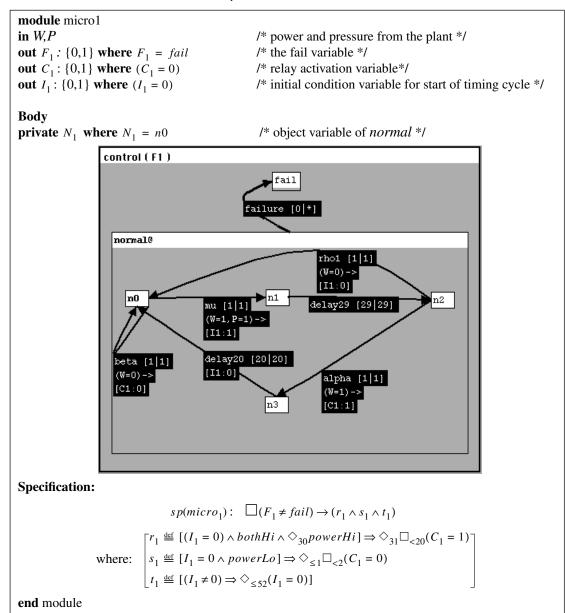

| FIGURE 10. | Control module                                                  | 35 |

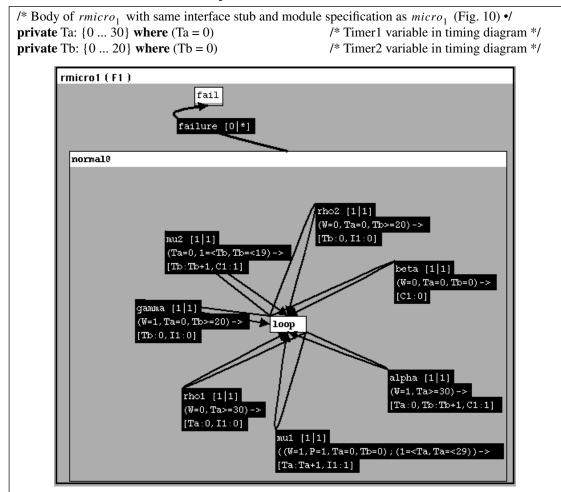

| FIGURE 11. | Refinement of microprocessor control module                     | 37 |

# **1.0 Introduction**

*Reactive* systems exhibit ongoing, possibly non-terminating, interaction with the environment. *Real-time* systems are reactive systems that must satisfy quantitative timing constraints. This paper presents a structured compositional design method for discrete real-time systems that can be used to combat the combinatorial explosion of states in the verification of large systems.

A system is decomposed into parallel components called *modules*. A *composition rule* describes how the correctness of the system can be determined from the correctness of its modules, without knowledge of their interior structure. The advantage of compositional verification is clear. Each module is both simpler and smaller than the system itself.

In addition to system decomposition, an abstract specification of a module may need to be refined into implementations closer to code. A *refinement rule* guarantees that specifications of abstract modules are preserved by their implementations.

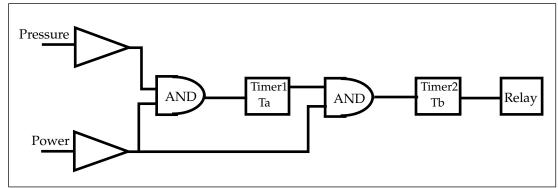

The *StateTime* toolset is used to automate parts of compositional designs using a combination of model-checking and simulation. The design method is illustrated using a reactor shutdown system that involves the use of three microprocessors, each independently checking sensor readings, with the final decision to shut down based on a majority vote. The single microprocessor version can be checked in the StateTime toolset without compositional reasoning. However, the three-microprocessor system suffers from a combinatorial explosion of states and a compositional approach is thus needed. The reactor example also illustrates the use of the refinement rule.

The compositional design method is based on the TTM/RTTL framework [36,37,40] which consists of the following:

- A *constructive description language* called timed transition models (TTMs) for describing reactive systems. A TTM is a guarded transition system with lower and upper time bounds on the transitions that relate to the occurrence of a special clock transition *tick*. Concurrent real-time programs, nondeterministic timed Petri nets and diverse mechanisms for timing, synchronization and communication constructs can be converted into TTMs in a straightforward manner.

- A *declarative specification language* called real-time temporal logic (RTTL) for describing the requirements that a TTM should satisfy without discussing how the TTM is constructed. RTTL is a timed extension of linear temporal logic augmented with a transition variable for describing TTM events.

- Analysis techniques for demonstrating that a TTM conforms to its specification. Modelchecking and a proof system for theorem proving are the main analysis techniques. Model-checking is a method for automatically verifying concurrent systems in which a finite-state model of the system (TTM) is compared with a correctness requirement (RTTL). Since time is a monotonically increasing variable, the state-space of naive timed systems is automatically infinite state. Hence, special care is taken in the modelchecking algorithms to keep the state space finite provided the data types are finite.

- A toolset called *StateTime* [38] which has a *visual* statechart-like *executable* language for representing TTMs hierarchically. An automatic translator to the model-checker and theorem prover STeP [31] allows for analysis. Although STeP is designed for untimed

systems, the automatic translation is done in such a way so as to allow for the use of STeP's model-checking facilities. The STeP theorem prover can also be used for simplifying properties.

The TTM/RTTL framework was initially conceived for the analysis of *closed* systems whose behaviour is completely determined by the state of the system itself [17]. In a closed system, we assume that the environment may set the initial values of input variables, but, once the system starts running the environment cannot modify any of the system variables. Thus, all changes to the system variables are accounted for by the transitions of the program. By contrast, reactive systems are best thought of as *open* systems whose behaviour depends on continuous interaction with the environment. We provide below an informal sketch of how the framework is extended to the open setting. The concepts will be made precise in the sequel.

This paper defines the notion of an open real-time reactive *module* m = [i, b, s] where *i* is the module *interface stub* (e.g. variables or channels shared with the environment), *b* its *body* (a TTM) and *s* the module *specification* (an RTTL formula in the interface variables). The module specification *s* must hold for all module computations including arbitrary changes that the environment might make at any time to the interface variables. The composition of two modules  $m_1 || m_2$  is also a module.

Not all parts of a module are always determined. For example, the interface stub and specification may be given, but not the body. We denote a module with an unspecified body by  $[i, \bullet, s]$ . A Composition Rule (justified in the sequel) given by

**Composition Rule:**

$$\begin{array}{c} m_1 \vDash s_1 \\ m_2 \vDash s_2 \\ (s_1 \land s_2) \rightarrow r \end{array} \right\} m_1 \parallel m_2 \vDash r$$

states that if each of the modules satisfy their respective specifications, then the system satisfies its global requirement r provided the requirement can be derived from the conjunction of the module specifications. The composition rule allows for both bottom-up and top-down design. In the bottom-up method, the independently designed and implemented modules (with respective specifications  $s_1, s_2$ ) when brought together exhibit the emergent property r provided ( $s_1 \land s_2$ )  $\rightarrow r$ .

In top-down development, the system under design (*sud*) that is required to conform to a global system requirement r can be decomposed into modules  $m_1 = [i_1, \bullet, s_1]$  and  $m_2 = [i_2, \bullet, s_2]$  provided  $(s_1 \land s_2) \rightarrow r$ . At this stage, we have not yet committed to module implementations. Each of these modules can then be given to a programmer whose job it is to develop a body that satisfies the module specification.

The body of module  $m_1$ , whose variables can be reduced to finite ranges, can be shown to satisfy its module specification (i.e.  $m_1 \models s_1$ ) by model-checking provided the effects of the environment are taken into account. The proof of  $(s_1 \land s_2) \rightarrow r$ , except in the simplest of cases, requires the use of deductive techniques (RTTL theorem proving). Thus the composition rule usually involves a combination of algorithmic and deductive techniques.

It is advisable that the programmer design and code the body of a module at as high a level as possible (using TTMs). This keeps the body simple and small which makes it understandable and prevents state explosion. There is then a need to *refine* the high-level module body into a TTM that is closer to implementation. For example, an abstract TTM

may directly specify a delay of 50 ticks, but the implementation on a microprocessor might be a loop construct that increments a counter every traversal of the loop. The internal loop and counter are unobservable to an external agent interacting with the module as the agent can only observe changes in the interface variables.

Two modules with the same interface are observationally equivalent (written:  $m_1 \approx m_2$ ) if they agree on timed observations of their interface variables. Under suitable conditions (presented in the sequel) a Refinement Rule states that:

**Refinement Rule**:  $m_1: [i, b_1, \bullet]$  $m_2: [i, b_2, \bullet]$  $m_1 \approx m_2$   $(m_1 \models s) \equiv (m_2 \models s)$  for any module specification s.

Hence, if  $m_2$  is observationally equivalent to  $m_1$ , then  $m_2$  can replace  $m_1$  wherever it occurs with a guarantee that any module specification *s* will be preserved. There are efficient polynomial algorithms for checking observational equivalence of finite state systems, and equivalence preserving transformations are available for refining infinite state systems.

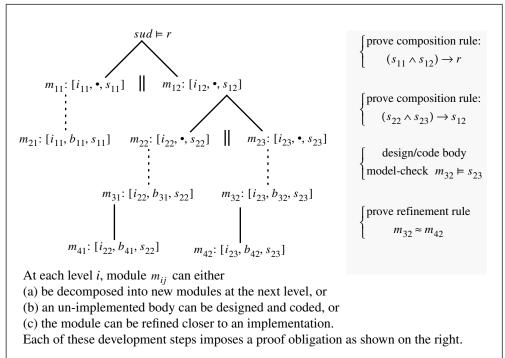

Given a requirement r that a system *sud* must satisfy, the composition and refinement rules allow for a systematic modular development method represented by the tree in Fig. 1. Each step imposes a proof obligation as shown in the right hand column of the fig-

#### FIGURE 1. Structure diagram for compositional design method

ure. The process continues until all the modules have bodies that can be directly coded into the given program language. We need not adhere to the ordering suggested by the figure. For example, the complete implementation of  $m_{11}$  can take place before the other modules are designed. It is also possible to reverse-engineer already implemented code and move bottom-up.

We proceed as follows in the rest of this paper. In section 2 we provide background information needed to understand the TTM/RTTL framework and the StateTime toolset. Section 3 defines the notion of a module, modular validity and the composition rule. It also describes how conditional specifications can be used to constrain module environments. Section 4 presents the refinement rule for modules based on the notion of observational equivalence of TTMs developed in [26]. Observational equivalence of TTMs will be defined precisely in the sequel, but the reader is referred to [27] for a set of TTM equivalence preserving transformations and to [28] for an efficient polynomial time algorithm to check TTM observational equivalence. Module observational equivalence is defined in such a way that the TTM results can be applied directly to module equivalence as well. In Section 5, we use the composition and refinement rules for the structured design of a reactor shutdown system. The design method is also discussed in some detail (Sect. 5.6). Comparisons to other approaches and concluding remarks are presented in Section 6.

# 2.0 Background

In the sequel, we use relative quantification (Qx:T|R:P) where Q is a quantifier  $(\forall \text{ or } \exists)$ , T is the type of the dummy variable x, R is the range of the dummy variable and P a predicate [14]. For example,  $(\forall i:int|3 \le i:P)$  means "for all values of an integer variable *i*, if *i* is at least as large as 3 then *i* has property P". If no range is supplied then it is *true*. The notation d:D generally means that  $d \triangleq D$ . For example,  $f:(\exists d:int|d > 0:x + d \le 4)$  means that we are defining f by  $f \triangleq (\exists d:int|d > 0:x + d \le 4)$ . In TTM update functions (see sequel), d:D denotes assignment, i.e. d:=D.

### 2.1 Real Time Temporal Logic (RTTL)

Linear time temporal logic [32] uses temporal connectives such as  $\Box$  (henceforth),  $\bigcirc$  (next),  $\diamondsuit$  (eventually),  $\mathfrak{U}$  (until) and past operators such as  $\bigcirc$  (previous state) to represent qualitative temporal properties. The standard connectives are applied to *state-formulas* (which are the atomic predicates) to obtain temporal logic formulas.

Real-time temporal logic (RTTL) is obtained by adding a fair *tick* transition and the ability to refer to system transitions via a distinguished transition variable. We refer the reader to [32] for a precise discussion of standard temporal logic and to [37,40] for real-time temporal logic. We now provide a brief review of some of the basic concepts.

Let x and y be the system variables where the type of x is the integers and y has a set type. An example of a state-formula f is  $(\exists d:int | (x + d \le 4) \land (7 \in y))$ . In this formula, the bound variable d is just a dummy variable and is not considered a system variable. A state is a mapping from the system variables to values in their relevant types. Since f evaluates to true in the state given by  $s = \langle x:2, y: \{7, 9\} \rangle$ , we write  $s \models f$  (state s satisfies f), and we call s an f-state.

A temporal logic formula such as  $\Diamond f$  ("eventually *f* is true") cannot be interpreted in a single state; rather it is evaluated in an infinite sequence of states  $\sigma$  given by  $\sigma = s_0 s_1 s_2 \dots s_i \dots$  where  $\sigma \models \Diamond f$  (" $\sigma$  satisfies  $\Diamond f$ ") will mean that there is at least one state subsequent to the initial state that is an *f*-state. An inductive definition of the satisfaction relation  $\models$  can then be given. Let  $(\sigma, i) \models f$  denote the satisfaction of temporal formula *f* at a position  $i \ge 0$  of the sequence  $\sigma$ . For a state-formula *f*,  $[(\sigma, i) \models f] \triangleq [s_i \models f]$ .

We can then give the appropriate inductive definitions for the propositional connectives (e.g. negation, conjunction, implication) followed by the usual definition of the temporal operators. For example, for temporal logic formulas *g* and *h*, the *until* operator is defined by  $[(\sigma, i) \models g^{\circ}Uh] \triangleq (\exists j | j \ge i:(\sigma, j) \models h \land (\forall k | i \le k < j:(\sigma, k) \models g))$ . For an arbitrary temporal logic formula *f*,  $\sigma \models f$  is an abbreviation for  $(\sigma, 0) \models f$ . A formula *f* is *generally-valid* iff  $(\forall \sigma | \sigma \models f)$ .

The implication  $(f \to \Diamond g)$  states only that "*f* implies eventually g" at the initial position of the computation, i.e. if *f* holds at the initial position then there is a subsequent position where *g* holds. As a notational convenience, we will write  $f \Rightarrow \Diamond g$  for  $\Box(f \to \Diamond g)$  which states that the implication holds at *all* positions of the sequence. In general, the double arrow *entails* operator is defined by  $[p \Rightarrow q] \triangleq \Box[p \to q]$  for any temporal logic formulas *p* and *q*.

We need the notion of *timed transition sequences* for the description of real-time systems. Since we envisage that a *transition*  $\tau_i$  causes a transfer from state  $s_{i-1}$  to state  $s_i$ , we may rewrite the infinite sequence of states  $\sigma = s_0 s_1 s_2 \dots$  as:

$$\sigma = (\tau_0, s_0)(\tau_1, s_1)(\tau_2, s_2)...$$

(Eq. 1)

The start transition  $\tau_0$  (e.g. a computer reboot) puts the system in state  $s_0$ . The transition  $\tau_1$  takes the system from state  $s_0$  to  $s_1$  and so on. We give the initial transition  $\tau_0$  the special name *start*. The distinguished variable  $\varepsilon$  (the *transition variable*) is always part of the state. The transition variable is used to record the last event taken, i.e. for the sequence  $(start, s_0)(\tau_1, s_1)(\tau_2, s_2)...$  we have that  $s_0(\varepsilon) = start$  and  $(\forall i | i > 0:s_i(\varepsilon) = \tau_i)$ . The reason we need a *start* transition is so that  $\varepsilon$ , like all other state variables, has an initial value.

The transition variable can be used to refer directly to event occurrences. For example, for a traffic system, the temporal logic formula ( $\varepsilon = turn\_red$ )  $\Rightarrow \Diamond(\varepsilon = turn\_green)$  asserts that anytime the light turns red, it must eventually turn green.

In order to represent time, we introduce the special transition *tick*. A timed sequence  $\sigma$  must satisfy the *ticking constraint* which asserts that there are an infinite number of ticks occurring in the sequence, i.e.  $\sigma \models \Box \diamondsuit (\epsilon = tick)$ . Thus, time must progress irrespective of what happens in a system or its environment. It is possible for any finite number of transitions to occur between two ticks of the clock.

We may use quantified Manna-Pnueli temporal logic to define the bounded real-time until operator,  $p \mathcal{A}_{[l,u]}q$ , which in turn can be used to express a variety of important realtime properties. Informally<sup>2</sup>, the meaning of the bounded until operator is that eventually q will occur at a time between l and u ticks from now; until then q must hold. Other bounded operators can then be defined as follows:

| $\Diamond_{[l, u]} p$ | def | $(true \mathcal{U}_{[l,u]} p)$ | Bounded response: $p$ must hold after the $l$ -th tick but before the $(u + 1)$ -th tick. |

|-----------------------|-----|--------------------------------|-------------------------------------------------------------------------------------------|

| $\diamond_{\leq u} p$ | def | $\langle 0, u \rangle p$       | p must hold before the $(u + 1)$ -th tick.                                                |

<sup>2.</sup> Formally, the *bounded until* operator is defined using a *flexible* clock variable *t* (that is incremented by one every time the clock ticks), and a *rigid* time variable  $t_0$  (that retains the same value over all states) as follows:  $p\mathcal{U}_{[l,u]}q \triangleq (\forall t_0:type(t)|(t = t_0) \rightarrow p\mathcal{U}(q \land (t_0 + l \le t \le t_0 + u)))$ . Please refer to [36,40] for the precise details. Since the bounded time operators are defined using ordinary quantified temporal logic, the untimed temporal theorem prover STeP [31] can be used to show the validity of theorems such as  $\Diamond_0 \Diamond_2 p \equiv \Diamond_2 p$ , which can, in principal, be used for the deductive reasoning in the sequel.

$\Box_{<l}p \qquad \stackrel{\text{def}}{=} \quad (p\mathfrak{U}_{[l,\infty]} true) \qquad Bounded invariance: p \text{ must hold until the } l \text{ -th tick.}$  $\diamond_d p \qquad \stackrel{\text{def}}{=} \quad (true\mathfrak{U}_{[d,d]}p) \qquad Exact time: p \text{ is true in exactly } d \text{ ticks.}$

The formula  $\diamond_0 p$  asserts that p will hold before the next tick of the clock. Several state changes can occur before p occurs without the clock advancing. The  $\diamond_0$  operator can often be used in place of the *next* operator where there is a need for stuttering-invariant formulas, i.e. formulas that are "robust" with respect to unobservable moves of the environment. Some further examples of clocked properties are:

- $p \rightarrow (q \mathcal{U}_{[3, 7]} r)$ : If p holds initially, then eventually between 3 and 7 ticks r holds, and q must hold continuously until then. This property is asserted only at the initial position.

- $\Box(p \to (q \mathfrak{A}_{\leq 4} r))$ : Every position satisfying p is followed within 4 ticks by r, and q holds continuously until then.

- p ⇒ ◊<sub>0</sub>□<sub><2</sub>q: If p holds at a position, then at some subsequent position before the next clock tick there should be the start of an interval of duration 2 ticks during which q holds continuously.

- $\Box(p \to \Box_{<3} \neg q)$ : The property q cannot become true sooner than 3 ticks after any occurrence of the property p.

We often need to compare expressions in consecutive states. We therefore introduce an abbreviation for the next value of a variable v, written v'. For example, the formula  $\Box(v' > v)$  asserts that the value of v is greater in every successor state that it is in its immediate predecessor (see [32] for the precise details).

# 2.2 Timed Transition Models (TTMs)

TTMs are timed extensions of the fair transition systems of Manna and Pnueli [32]. The extension involves lower and upper time bound constraints on transitions, that refer to the number of occurrences of the special transition *tick*. A TTM *M* is defined as a 4-tuple M = (V, I, T, F) as follows:

- *V*: a finite set of typed *system variables*. The distinguished transition variable  $\varepsilon$  is always in *V*, where  $type(\varepsilon) = T$ . The variables set also include control and data variables that are used to describe the various parts of *M*. Each state of *M* is a map from *V* to its types; the set of all states is denoted by  $\Sigma_M$  (or just  $\Sigma$  when it is clear what the TTM is).

- *I*: the *initial condition*. This is a satisfiable boolean valued expression in the system variables that characterizes the states at which the execution of the TTM can begin. A state *s* satisfying *I* is called an *initial state*.

- *T*: a finite set of transitions which includes the distinguished transitions start and tick. Each transition τ ∈ T is a function τ:Σ → powerset(Σ) that maps a prestate s in Σ to a (possibly empty) set of τ-successor states τ(s) ⊆ Σ. An empty successor set means that the transition is disabled (i.e. cannot be taken from the prestate). A successor state s' is also called a poststate of τ from s. If the set of successor states consists of a single poststate, then the transition is deterministic. If there is more than one poststate, then the transition is nondeterministic.

• *F*: a *fairness set* where  $F \subset T$ . Informally, the fairness constraint for each transition  $\tau \in F$  disallows computations in which  $\tau$  is enabled infinitely often but is taken only finitely many times<sup>3</sup>.

Since, in general, we do not need nondeterministic transitions<sup>4</sup>, we can also describe a transition  $\tau$  by its *enabling condition*  $enb(\tau)$  (the condition under which the transition becomes eligible to be taken), and a simultaneous *update function*

$$upd(\tau) = \{v_1: e_1, v_2: e_2\}$$

where  $e_1$  and  $e_2$  are expressions in the system variables, which indicates that the values of  $v_1, v_2$  in the poststate s' are  $s(e_1), s(e_2)$  respectively, where s is the prestate. No other system variables (e.g.  $v_3$ ) are changed. The transition  $\tau$  is *enabled* in a state s (written:  $s \models enb(\tau)$ ) if  $\tau(s) \neq \emptyset$  — otherwise  $\tau$  is said to be *disabled*.

The transition  $\tau$  can be fully characterized by a *transition relation*  $\rho_{\tau}$  given by  $\rho_{\tau}$ :  $enb(\tau) \wedge (v_1' = e_1) \wedge (v_2' = e_2) \wedge (v_3' = v_3)$  which is a predicate in the primed and unprimed system variables. Primed variables refer to the value of the variables in the poststate, and unprimed variables refer to values in the prestate (see [32] for precise details). By convention, we leave out conjuncts such as  $(v_3' = v_3)$  for which there is no change.

In addition to the enabling condition and update function, we associate with each nontick transition  $\tau$  a lower time bound  $low(\tau)$  and an upper time bound  $hi(\tau)$ , where  $0 \le low(\tau) \le hi(\tau) \le \infty$ . We allow bounds  $\tau[0, 0]$  and  $\tau[0, \infty]$  but not  $\tau[\infty, \infty]$ . The meaning of these bounds will be defined formally in the sequel, but we first provide an informal overview.

A timed transition  $\tau[l, u]$  with lower time bound *l* ticks and upper time bound *u* ticks, must delay *l* ticks before being taken, but must be taken by *u* ticks of the clock, provided it remains continuously enabled, and is not disabled by the occurrence of another transition that might have the effect of disabling  $\tau$ .

The operational semantics of TTMs will be described by the set of all its behaviours called *trajectories*. Informally, a trajectory is a timed sequence of states that starts in an initial state satisfying the initial condition of the TTM. From any state of the computation, any enabled transition is taken *in one atomic step*. Either a *tick* transition is taken at each step, in which case time advances, or a non-tick transition is taken, in which case time stays the same. The resulting interleaving of enabled transitions allows us to model concurrent processes<sup>5</sup>. When the transitions are taken, they update the variables according to the transition update function. The clock must tick infinitely often in any computation, and

<sup>3.</sup> Fairness is defined more formally in the sequel. A weaker notion of fairness than the one defined in this paper is called *justice* [32]. Fairness ensures that in interleaved parallel processes, the processes progress independently (fairness distinguishes concurrency from nondeterminism). The stronger notion of fairness defined in this paper is needed for the *tick* transition.

<sup>4.</sup> There is one exception to the rule. When  $choose(v_1, v_2)$  is used in transition updates it assigns arbitrary values to  $v_1$  and  $v_2$  in their appropriate types. No assumptions are made about the probabilistic distributions of the values assigned. This is a purely nondeterministic update that says any value in the type is possible in the successor state. This notion will used to construct environments of modules (Sect. 3.0).

<sup>5.</sup> Actual systems may have *overlapped* rather than interleaved execution. However, provided an appropriate fair set of transitions with the right level of atomicity is chosen, the interleaving model can accurately describe overlapped execution (see [32, p103] for further discussion).

an arbitrary but finite number of (non-tick) transitions can be taken between any two ticks of the clock. The lower and upper time bounds of transitions must be respected.

A computation  $\langle \tau_0, s_0 \rangle \langle \tau_1, s_1 \rangle \langle \tau_2, s_2 \rangle \dots$  of a TTM M = (V, I, T, F), where  $\tau_i \in T$  for  $i \ge 1$  and  $\tau_0 \stackrel{\text{def}}{=} start$ , is a timed sequence satisfying the three constraints below. In each case, we show how to write the constraint as a temporal logic formula.

- 1. *Initialization constraint*: The first state of the computation satisfies the initial condition, i.e.  $s_0 \models (I \land (\varepsilon = start))$ . The initialization constraint is thus represented by the temporal logic formula  $init(M) \triangleq I \land (\varepsilon = start) \land \bigcirc \Box (\varepsilon \neq start)$ . The transition *start* occurs once at the beginning of the computation and never again.

- 2. Succession constraint:  $(\forall i | i \ge 0: s_{i+1} \in \tau_{i+1}(s_i))$ , i.e. every prestate at position *i* must have as its successor a poststate according to the update function of  $\tau_{i+1}$  (the transition taken at position *i*). The succession constraint can be expressed in RTTL as  $succession(M) \triangleq \Box(\exists \tau: T | \rho_{\tau})$ , where  $\rho_{\tau}$  is the transition relation for  $\tau$ .

- Fairness constraint<sup>6</sup>: For each transition τ in the fairness set, it is not the case that τ is infinitely often enabled beyond some position in the trajectory, but taken at only finitely many positions in the trajectory. The fairness constraint can be written in temporal logic as *fair(M)* def (∀τ:F|□◊enb(τ) → □◊(ε = τ)).

A *timed sequence* that satisfies the above three constraints is called a *computation* of M. A computation describes the behaviour of a Manna-Pnueli fair transition system (enhanced with the *tick* of timed sequences). To describe the behaviour of timed transition models, we further constrain computations by lower and upper time bound constraints and call the resulting computations *trajectories*.

- 4. *Lower bound constraint:* for every transition  $\tau$  with lower bound l > 0, if  $\tau$  is taken at position *j* of the computation, then there must exist a prior position i < j so that there are at least *l* ticks of the clock between *i* and *j*, and  $(\forall k | i \le k < j: s_k \models enb(\tau) \land \varepsilon \neq \tau)$ , i.e.  $\tau$  is enabled but not taken in the states  $s_j \dots s_j$ .

- 5. Upper bound constraint: for every transition  $\tau$  with upper bound  $u \neq \infty$ , if  $\tau$  is enabled at position *j* of the computation, then there must exist a subsequent position  $k \ge j$  with no more than *u* ticks of the clock between *j* and *k*, such that either  $\tau$  is taken or disabled at position *k*.

As with the initialization, succession, and fairness constraints, both the bound constraints can also be described in RTTL. For a non-tick transition  $\tau$  with lower time bound *l* (where l > 0) and upper time bound *u*, the bound constraint is:

$$bound(\tau) \stackrel{\text{def}}{=} moe(\tau) \Rightarrow [\Box_{(Eq. 2)$$

<sup>6.</sup> The fairness constraint is included for generality but is not necessary for the example developed in the sequel. However, real-time systems may have requirements where fairness is useful. For example, there may be a requirement to log every error to a file or printer; this does not have to happen within a precise time as the requirement may merely be that the error is eventually logged. In the Fischer protocol, mutual exclusion is ensured if certain precise timing constraints are satisfied; however, for response it may be sufficient to specify that each process eventually returns to it's non-critical region. For TTMs, we allow in increasing stringency: spontaneous τ[0, ∞] transitions, fair transitions and timed transitions. This allows us to describe systems to the appropriate precision.

where  $moe(\tau) \triangleq enb(\tau) \land [\varepsilon \in \{start, \tau\} \lor \ominus \neg enb(\tau)]$ , and where  $\ominus p$  (the *previous* temporal operator) holds at a position *j* of a trajectory provided *j* is not the first position of the trajectory and *p* holds at position j-1. If l = 0, then the left conjunct  $\Box_{<l}[\bigcirc(\varepsilon \neq \tau)]$  is replaced by *true*. If  $u = \infty$ , then the right conjunct of the consequent in (Eq. 2) is replaced by *true*. The bound constraint (for both lower and upper bounds) can be written in temporal logic as:

$$bound(M) \stackrel{\text{def}}{=} (\forall \tau: T | bound(\tau)).$$

(Eq. 3)

The moment of enablement  $moe(\tau)$  describes the relevant positions of a computation at which the bound constraint for a transition  $\tau$  (that is enabled at that position) must be asserted. A relevant position is either the initial position ( $\varepsilon = start$ ), or a position at which the transition has just been taken ( $\varepsilon = \tau$ ) and is re-enabled, or a position where  $\tau$  has just become enabled ( $enb(\tau) \land \ominus \neg enb(\tau)$ ).

Once a transition  $\tau$  becomes enabled at some position, it begins to "mature" but cannot be taken until its lower time bound number of ticks has been taken, at which point the transition becomes "ripe" for execution. If the transition is continuously enabled during maturation, then it can be taken any time after it becomes ripe, but it must be taken or become disabled before the upper time bound number of ticks has expired. Thus, transitions "mature" together as time advances but execute separately in an interleaving manner.

As noted above, the initialization, succession, fairness and bound constraints can be expressed in RTTL. The formula des(M) defined by

$$des(M) \stackrel{\text{def}}{=} init(M) \land succession(M) \land fair(M) \land bound(M)$$

(Eq. 4)

fully describes the set of all trajectories of the TTM M.

Since a trajectory of a TTM *M* is a timed sequence, the trajectory must also satisfy the ticking constraint ticking(M):  $\Box \diamondsuit (\varepsilon = tick)$ . However, there is the possibility of a conflict between the upper bound and the ticking constraint (in which case no timed sequence will satisfy des(M) and the ticking constraint simultaneously). This happens in the presence of *immediate* transitions of the type  $\tau[0, 0]$  that are self-loops — such a  $\tau$  is taken repeatedly yet the tick transition is delayed indefinitely<sup>7</sup>. This is called a Zeno computation and the TTM is said to exhibit *Zeno behaviour*. Any cycle of transitions whose elements are all immediate may also exhibit Zeno behaviour. A TTM that exhibits Zeno behaviour cannot be implemented, and hence we must find ways to ensure that our systems are non-Zeno.

The problem of Zeno computations can be avoided by disallowing self-looping immediate transitions. However, immediate transitions are useful for modelling "instantaneous" (i.e. before the clock ticks) reactions. If immediate transitions are used in a TTM *M*, then we must check for the validity of  $\Box \diamondsuit (\varepsilon = tick)$  in every single computation that satisfies the bound constraints. Fortunately, for those systems where model-checking can be used, the ticking property can be verified automatically (e.g. see Table 1 in Sect. 5.5). *In the*

<sup>7.</sup> The StateTime tool automatically converts TTMs to fair transition systems [39] that can then be analyzed using STeP (see Sect. 2.4). In this conversion, additional conjuncts are added to the enabling condition of the *tick* transition that disables the tick transition when an urgent timed transition must be taken. In a system with a selfloop  $\tau$ [0, 0] transition, the *tick* transition is disabled indefinitely. This reflects the conflict between the ticking constraint and the upper time bound constraint. The conversion procedure does declare tick to be fair. However, since *tick* is disabled until the urgent transition is taken, the fairness constraint is satisfied despite the fact that *tick* is not taken.

*sequel, we assume that all TTMs are non-Zeno*. This is not restrictive at all for the examples of this paper because all TTMs can be model-checked to ensure that they are non-Zeno.

The set of all trajectories of a TTM *M* is denoted by traj(M). If a trajectory  $\sigma$  satisfies a temporal logic formula *p*, then we write  $\sigma \models p$ . If an RTTL formula *p* is satisfied in all trajectories of *M* (i.e.  $(\forall \sigma: traj(M) | \sigma \models p)$ ), then we write  $M \models p$ , and the formula *p* is said to be *M*-valid. Any generally-valid formula is also *M*-valid. Any trajectory in traj(M)always satisfies des(M); hence, the transition system *M* and the temporal logic formula des(M) are two equivalent ways of describing traj(M).

**Theorem 1:** For any (non-Zeno) TTM *M* and RTTL formula *p* in the variables of *M*: (a)  $[M \models p] \equiv [\models des(M) \rightarrow p]$ , and (b)  $M \models des(M)$ .

If we treat des(M) as an axiom of the RTTL logic, then (Th. 1)(a) describes the relative completeness of the logic for proving *M*-validities. An oracle is a device that is guaranteed to provide a proof of any generally-valid RTTL formula. Hence to prove the *M*-validity of *p* it is sufficient to submit to the oracle the formula  $des(M) \rightarrow p$ . While the axiom des(M) is theoretically adequate it is not very practical. In practice the special proof rules in [36] and model-checking (Sect. 2.4) are the preferred methods for proving *M*-validities.

### 2.3 Parallel composition of TTMs

The parallel composition  $M_1 \parallel M_2 = (V, I, T, F)$  of two TTMs  $M_1 = (V_1, I_1, T_1, F_1)$ and  $M_2 = (V_2, I_2, T_2, F_2)$  is defined in [40] by:

•

$$V = V_1 \cup V_2$$

,

•  $I = I_1 \wedge I_2$  provided  $I_1 \wedge I_2$  is satisfiable,

- $T = T_1 \cup T_2$  where  $\{start, tick\} \subset T_1 \cap T_2$  and hence  $\{start, tick\} \subset T$ , and

- $F = F_1 \cup F_2$  where  $tick \in F_1 \cap F_2$ . We call  $M_1 \parallel M_2$  the composite TTM.

The above definition holds for shared variables but must be slightly modified for synchronized transitions or channels as described in [40]. Both  $M_1$  and  $M_2$  synchronize with respect to the *start* and *tick* transitions. The *tick* transition thus provides the composed system with a uniform notion of time.

### 2.4 Overview of the StateTime toolset

The StateTime toolset assists the user (a) to describe devices and systems using a graphical structured language, (b) to execute the description so as to validate that the description is a reasonable model of the actual system, and (c) to check that the description conforms to its requirements using model-checking. We give a brief description below of the main features of the toolset needed for the sequel. The reader is referred to [38] for a more complete description.

The main parts of the toolset of interest to us are the *Build* tool and its translator to the theorem prover and model-checker STeP [31]. The Build tool is a window-based front end for constructing compact visual models of real-time systems called TTMcharts. TTM-charts resemble statecharts, but with a simpler semantics and with the additional feature

that transitions may have time bounds. We often use the terms TTMcharts, charts and TTMs interchangeably as the semantics of TTMcharts is based on TTMs.

A chart is a hierarchy of *objects*. Objects describe control information and impose structure on the operation of the system. An object is either *primitive*, *parallel* (called AND in statecharts) or *serial* (XOR in statecharts). A primitive object has no internal structure. A parallel object is constructed from a collection of child objects (or sub-objects) by parallel composition. The parallel composition of child object via an event causes the simultaneous entry into each of the child objects. The exit from the object causes the simultaneous exit from all its children. A serial object is constructed from a collection of child object causes the simultaneous exit from all its children. A serial object is constructed from a collection of child objects operates in all objects such that only one of the children operates at a time. The entry and exit from a serial object via an event causes the simultaneous entry and exit of the currently operating child object.

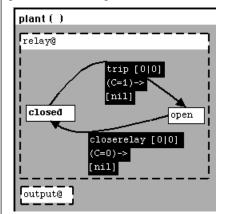

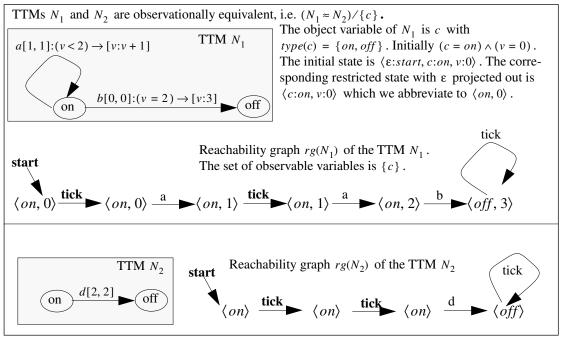

Charts may have *data variables* which are tested and set by events. Each non-primitive serial (XOR) object has an *object variable* which is used to indicate which of its children is currently operating. As an example, consider the *plant* chart (Fig. 2) which will be described in more detail in Sect. 5.2. The plant is the parallel composition of two children called *relay* and *output* which we write as plant = relay || output. The serial object *relay* has two children *closed* and *open* which are primitive. Zooming in to the *output* object indicates that it is the serial composition of the primitive object *wait* and the sub-object *update*. The *update* object is the parallel composition of the *pressure* and *power* sub-objects which is where the pressure and power sensor values are updated.

The top-level objects *relay* and *output* have object variables *R* and *D* respectively where  $type(R) = \{closed, open\}$  and  $type(D) = \{wait, update\}$ . The state-formula defined by  $(R = closed \land D = wait)$  describes a state in which the relay is closed and the next sensor update is two ticks away. The pressure *P* and power *W* are examples of data variables.

A serial object begins execution at its *default* indicated in bold; e.g. the default for the *output* object is *wait* (Fig. 2). Once a *cycle[0,0]* event is taken in the *output* object, nothing else can happen until two ticks of the clock are taken. After two but before the third clock tick, the *endupdate[2,2]* event *must* occur (in this case, there are no other events to preempt its occurrence). Before *endupdate* occurs, the pressure and power, or just one of them, or no update at all *may* occur. The source of the *endupdate* event is the structured object *update*; hence *endupdate* can be taken, no matter where execution in *update* currently resides, and preempts the internal events of *update*.

A user can describe systems incrementally by composing sub-objects together to form a super-object (bottom-up), or by decomposing a object into further sub-objects (topdown). A chart can be executed at any point in the development cycle even before it is finally fixed using the interactive simulation tool. The simulation tool displays chart trajectories, and requires user interaction to select the transition to be taken at nondeterministic selection points. The Build tool automatically translates TTMcharts into fair transition systems according to the algorithm presented in [39]; STeP [31] can then be used to model-check the chart for conformance to its specification.

The current StateTime toolset was not meant for modular systems. It suffers from various deficiencies including the fact that it does not support interface stubs, automatic generation of module environments (Sect. 3.0) and refinement. It is easy to verify standard temporal properties, but an observer must be constructed for real-time properties. How-

#### FIGURE 2. Plant module

| module plant(C;P,W)                                                            |

|--------------------------------------------------------------------------------|

| <b>in</b> <i>C</i> : {0,1} <b>where</b> ( <i>C</i> = 0)                        |

| <b>out</b> <i>R</i> : {closed, open} <b>where</b> ( <i>R</i> = <i>closed</i> ) |

| <b>out</b> $P$ : {0,1} <b>where</b> ( $P = 0$ )                                |

| <b>out</b> $W$ : {0,1} <b>where</b> ( $W = 0$ )                                |

#### Body

private D: {wait,update}

/\* relay activation. (*C* = 1) causes the relay to open \*/ /\* Relay position variable \*/

- /\* pressure variable where (P = 1) is high pressure\*/

- /\* power variable where (W = 1) is high power\*/

The dotted lines in the TTM to the left indicate parallel composition, i.e. plant = relay || output. The "@" symbol in output@ indicates that it has further internal structure. Zooming into output@ produces the TTM bottom left. Zooming a further level down into update@ produces the TTM to the bottom right, which is where pressure and power updates take place.

The lower time bound of 2 in events *pH*i, *pLo* and *end-update* enforce the filtering assumption viz. pressure and power updates are no more frequent than once every two ticks of the clock. Before the third tick of the clock, the upper bound of *endupdate* causes a move back to *wait*, at which point there is another delay of two clock ticks before further sensor updates can occur.

ever, the tool is used in this paper for the construction of modules, their environments (done manually) and model-checking module properties. In principal, a chart when loaded into STeP can also be verified using theorem proving — however, theorem proving real-time properties proved tedious (especially on account of the need to use quantifiers). We are currently updating StateTime to fully support real-time modules and real-time formulas for both model-checking and theorem proving in a seamless fashion, based on the results of this paper.

# **3.0** Modules and module composition

Our notion of a module is based on the untimed reactive modules of Manna and Pnueli [32]. Although the Manna Pnueli framework has been used for real-time systems [23], the extension to their system for modules as delineated by Chang [8] is different to ours. The main differences are: (a) our modules are supported by a model-checker, (b) we provide a state-event refinement relation for modules, and (c) the reactive modules of [32] are not fully compositional as their parallel composition yields a transition system, not another module (composition of our modules yields another module). We now explain these differences in more detail.

Chang [8] advocates a restricted assumption/guarantee style, wherein the environmental assumption is stated as a restriction on the environment's next-state relation. He also presents a decision procedure in the propositional case and a deductive system for the discrete time metric temporal logic used for transition modules. Although Chang provides a deductive framework for real-time modules, he does not present model-checking algorithms and tools (which are crucial for the needs of this paper).

Chang's temporal operators are new; they are not expressed in ordinary untimed temporal logic. The transition modules of [8] must be self-disabling, i.e. once a transition is taken it cannot be again enabled (as in a self-loop). The TTM semantics of modules in this paper does not impose this restriction on module descriptions.

The untimed refinement relation of [32] will not work for real-time modules (as will be explained in Sect. 4.0). Hence, in Sect. 4.0, we introduce the necessary framework needed for real-time module refinement.

The reactive modules of [32] are not fully compositional as their parallel composition yields a transition system, not another module. In this section, we provide the notion of a fully compositional discrete time transition module (like [8]). This requires a more complete treatment of the notion of the interface stub and modes of variables in a module. It also allows our treatment to deduce the trajectories of the composite module given its sub-modules (Lemma 1), from which we obtain the notion that a module specification must be satisfied independently of the behaviour of the environment (Lemma 2), and finally yields the Composition Rule (Th. 2). By contrast, [32] starts with the notion of a module as given in Lemma 2 and then proceeds from there to obtain the Composition Rule.

A module m = [is(m), bd(m), sp(m)] is defined by its interface stub is(m), body bd(m) and RTTL specification sp(m):

- 1. The *interface stub* consists of the declaration of all the variables that are shared between module m and other modules in its environment (defined more precisely in Sect. 3.2). The stub also declares the initial values of all the shared variables. We let is(m) denote the set of shared variables.

- 2. The *body* bd(m) is a program whose statements may refer only to variables declared *private* to the body, or to variables in the interface. The set of private variables is denoted pr(m). In the sequel, the body is a TTM, in which case we let bd(m) denote the TTM with variables set  $is(m) \cup pr(m)$ . The initial condition init(m) is the conjunction of all the initial conditions declared on both the private and interface variables.

- 3. The *specification* sp(m) of the module is an RTTL formula in the shared interface variables. The specification asserts the required visible behaviour of the module.

In order to describe the behaviour of a module in an environment that may arbitrarily modify the interface variables  $is(m) = i_1, ..., i_n$ , we adjoin to the module TTM a spontaneous environmental transition  $\tau_E[0, \infty]$  defined by the update function  $choose(i_1, ..., i_n)$  (i.e. the interface variables can take on arbitrary values) while all the private variables remain unchanged, i.e.  $(\forall v: pr(m) | v' = v)$ . Thus the environmental transition may exhibit arbitrary behaviour, except that it may not modify any private variables of the module. However, shared interface variables may be changed at any point to any value in their respective types.

**Definition 1:** [*The TTM associated with a module*] The TTM  $\hat{m}$  associated with the module *m* is defined as  $\hat{m} = (V, init(m), T, F)$  where  $V = is(m) \cup pr(m)$  and  $T = T_{body} \cup \{\tau_E\}$  where  $T_{body}$  is the set of transitions of the body TTM, and  $F \subset T$  is the set of fair transitions of the body (note that  $\{start, tick\} \subset T$ ). Since  $\hat{m}$  is a TTM, we define  $traj(m) \stackrel{\text{def}}{=} traj(\hat{m})$  and  $des(m) \stackrel{\text{def}}{=} (\exists \bar{p} | des(\hat{m}))$  where  $\bar{p}$  is the set of all private variables, i.e variables in pr(m). (As before, we require that the timed transition model  $\hat{m}$  be non-Zeno).

The succession constraint of  $\hat{m}$  allows the body transitions to be interleaved in an arbitrary fashion with the environmental transition. The environmental transition thus simulates the behaviour of the module in an arbitrary context and allows the module to take stuttering steps in which none of the module private variables change from the prestate to the post-state.

The existentially quantified formula  $(\exists \bar{p} | des(\hat{m}))$  in (Dfn. 1) describes the same system as  $des(\hat{m})$  except with the private variables  $\bar{p}$  hidden, and thus this existential formula can be considered a description of m by abstract implementation [32, p.340]. In this style of description, we may choose the most straightforward implementation of the module mand describe its operational behaviour using a TTM (e.g. if m is a buffer, then a private list variable may be used to remember sequences of messages). What makes the implementation abstract is the existential quantification of the private variables. This means that we do not require or imply in any way that the real implementation of the module should contain any of these private variables (e.g. the list variable in the case of a buffer need not be used).

**Definition 2:** [*Modular-validity*] The RTTL formula *p* is modularly-valid for the module *m* (written  $m \models p$ ) iff  $(\forall \sigma : traj(m) | \sigma \models p)$ .

### **3.1 Parallel composition of modules**

Modules  $m_i$  (with variable sets  $V_i$ ) for i = 1, 2 are said to be *compatible* with each other if:

- each module has private variables that are not variables of the other module, i.e.  $pr(m_1) \cap V_2 = \emptyset$  and  $pr(m_2) \cap V_1 = \emptyset$ , and

- the conjunction of their initial conditions is satisfiable, i.e. *init*(m<sub>1</sub>) ∧ *init*(m<sub>2</sub>) is satisfiable, and

- the conjunction  $sp(m_1) \wedge sp(m_2)$  is satisfiable.

Compatible module composition,  $m = m_1 || m_2$ , is defined by  $m \leq [is(m), bd(m), sp(m)]$ where  $is(m) \subseteq is(m_1) \cup is(m_2)$ , i.e. some of the interface variables of the sub-modules may be hidden at the parent level.  $bd(m) = bd(m_1) || bd(m_2)$  is ordinary TTM composition (Sect. 2.2). Finally  $sp(m) = sp(m_1) \land sp(m_2)$ .

The private variables of the composite is  $pr(m) \stackrel{\text{def}}{=} pr(m_1) \cup pr(m_2)$ , and the initial condition is defined by  $init(m) \stackrel{\text{def}}{=} init(m_1) \wedge init(m_2)$ . The super-module  $m_1 \parallel m_2$  is itself a module; the TTM associated with this super-module is just the TTM obtained from  $bd(m_1) \parallel bd(m_2)$  together with the environmental transition that may change only variables in is(m) (i.e. it may not change any private variables).

In the next lemma, we assume that we have two modules  $m_1$  and  $m_2$ . If an environmental transition in a trajectory of module  $m_1$  has the same effect on its interface variables as a transition  $\tau_2$  of  $m_2$ , then we relabel the environmental transition in the trajectory to  $\tau_2$ , and the set of all the relabelled trajectories of  $m_1$  we call  $traj(\bar{m}_1)$ . A symmetric definition also provides us with the set  $traj(\bar{m}_2)$  of relabelled trajectories of  $m_2$ .

**Lemma 1:** If  $m = m_1 || m_2$  then  $traj(m) = traj(\overline{m}_1) \cap traj(\overline{m}_2)$ .

**Proof**: Let  $\sigma \in traj(m)$ . Trivially  $\sigma \models init(m_1)$  and hence the initialization constraint of  $m_1$  is satisfied. For the succession constraint, consider any position i of  $\sigma$ . Either the environment transition is taken at position i or some transition of m is taken. The environment transition of m may not modify any private variables of m and hence may also not modify private variables of  $m_1$ , so any environment step of m is also an environment step of  $m_1$ . If some transition of m is taken at position i, then it is either a transition of  $m_1$  or of  $m_2$  that is taken. Since no transition of  $m_2$  may modify private variables of  $m_1$ , a step taken by a transition of  $m_2$  (say  $\tau_2$ ) is the same as an environment step relative to  $m_1$  (the transition  $\tau_2$  must be renamed to an environmental transition). Thus at any position either a transition of  $m_1$  is taken or an environment transition of  $m_1$  is taken, and hence the succession constraint  $\sigma \models succession(m_1)$  holds. The fairness constraint of  $m_1$  is also satisfied, as any transition of  $m_1$  that is enabled infinitely often but not taken would also violate the fairness constraint of m. The ticking constraint of  $m_1$  is also satisfied, for suppose there is a position of  $\sigma$  beyond which there is no tick of the clock for  $m_1$ , then the ticking constraint for m would also be violated. If a transition of  $m_1$  violates its bound constraint, then the bound constraint on transitions of m will also be violated. Hence  $\sigma$  must also satisfy the bound constraint of m. Since  $\sigma$  satisfies the initialization, succession, fairness, ticking and bound constraints of  $m_1$ , it follows that  $\sigma \in traj(\overline{m}_1)$  holds. By symmetry it also follows that  $\sigma \in traj(m_2)$  holds. Thus  $\sigma \in traj(\overline{m}_1) \cap traj(\overline{m}_2)$ .

For the converse, let  $\sigma \in traj(\overline{m}_1) \cap traj(\overline{m}_2)$ . At any position of  $\sigma$  either a transition of  $m_1$  or of  $m_2$  is taken, in which case the same transition belonging m is taken, or an environment transition that is an environment transition of both  $m_1$  and  $m_2$  is taken. This environment step must also be an environment step of m as no private variables of  $m_1$  and  $m_2$  could have been changed. We can make similar arguments as before for the other constraints but in the converse direction. Hence  $\sigma \in traj(m)$ .

**Lemma 2:** Let modules  $m_1$  and  $m_2$  be compatible. Then

(a)  $[(m_1 \models sp(m_1)) \land (m_2 \models sp(m_2))] \rightarrow [(m_1 \parallel m_2) \models (sp(m_1) \land sp(m_2))]$ , and (b) For a module *m*,  $[m \models p] \rightarrow (m \parallel m') \models p$  for any compatible module *m'* and RTTL property *p*. **Proof**: Follows directly from Lemma 1. ■

Recall that a property is modularly-valid only if it is satisfied by all trajectories of the module. Lemma 1 tells us that the trajectories of the super-module are always a subset of those of its sub-modules. This means that a valid specification of a sub-module must also be valid for the super-module (Lemma 2a), and that a module specification remains valid no matter what the behaviour of its environment is, provided the environment respects the compatibility constraints (Lemma 2b).

### **Theorem 2:** [Composition Rule].

Let  $m_1$  and  $m_2$  be any two compatible modules and let the general-validity given by  $\models sp(m_1) \land sp(m_2) \rightarrow r$  hold. Then  $[m_1 \models sp(m_1)] \land [m_2 \models sp(m_2)] \rightarrow [m_1 \parallel m_2 \models r]$ .

**Proof**: Follows directly from Lemma 2 and temporal logic. ■

As mentioned in the introduction, the Composition Rule can be used bottom-up or topdown. In the bottom-up method, pre-existing implemented "off the shelf" modules can be combined into a super-module that satisfies a system requirement r. In the top-down method, we proceed as follows:

- 1. The system architect decomposes the system under design (*sud*) into modules  $m_1$  and  $m_2$  by:

- (a) designing compatible interface stubs  $is(m_1)$  and  $is(m_2)$ , and

- (b) designing module specifications such that  $sp(m_1) \wedge sp(m_2) \rightarrow r$ .

- 2. The architect gives each module interface and specification to a programmer. It is the job of the programmer to develop the module body so that the specification is modularly-valid. For example, if the programmer is given  $is(m_1)$  and  $sp(m_1)$  for the first module, he must design a body  $bd(m_1)$  so that  $m_1 \models sp(m_1)$  where the module  $m_1$  is fully described by  $m_1 = [is(m_1), bd(m_1), sp(m_1)]$ .

- 3. The required system is then  $sud = m_1 || m_2$  which is guaranteed by the Composition Rule to conform to the requirement r.

Parts of the development method can be automated by using a combination of modelchecking for proving modular-validity (step 2), and deductive theorem proving techniques can be used for proving that the system requirement is a consequence of the module specifications (step 1b).

A compositional proof has the following outline:

1.  $m_1 \vDash p_1$  $p_1$  is modularly-valid for  $m_1$  (by model-checking)2.  $m_2 \vDash p_2$  $p_2$  is modularly-valid for  $m_2$  (by model-checking)3.  $\vDash (p_1 \land p_2) \rightarrow r$ general-validity (deductive theorem proving)4.  $m \vDash r$ 1, 2, 3 and the Composition Rule where  $m = m_1 \parallel m_2$

In the sequel, we will leave out the module satisfaction symbol (except for its appearance in the last line) and write the above proof as:

- 1.  $p_1$  is modularly-valid for  $m_1$

- 2.  $p_2$   $p_2$  is modularly-valid for  $m_2$

| 3. | $(p_1 \land p_2) \to r$ | general-validity                                        |

|----|-------------------------|---------------------------------------------------------|

| 4. | $m \vDash r$            | 1, 2, 3 and the Composition Rule where $m = m_1    m_2$ |

By Lemma 2 (b), once we know that the context of the proof is the module m, then any specification of a sub-module of m will also hold for m, and hence there is no need to indicate which sub-module specification we are dealing with.

### **3.2 Modes of interface variables**

The interface stub of a module defined in the previous subsection consists of a set of typed shared variables with their initial conditions. We can provide more structure and flexibility to the interface specification which will enhance the user's ability to understand a module.

The additional structuring mechanism is provided by describing the *modes* of the shared variables. A variable in the interface stub is either **in** (the module body can read the variable but not write to it), **out** (the environment can read the variable but not write to it), or **share** (both the body and the environment have write access):

```

interface_stub ::= {mode {variables}<sup>+</sup> : type [where init]}*

mode ::= {in | out | share}

```

If a module *m* has a declaration "**out**  $y_1$ ", then no other module in the environment of *m* may have a writing reference to the variable  $y_1$ . If two (or more) modules each write to *y*, then they must each have the declaration "**share**  $y_1$ ", thus indicating that the external environment may also change  $y_1$ .

Let the variables in the interface stub be  $\bar{y} = y_1, ..., y_j, y_{j+1}, ..., y_k$ , where  $y_1, ..., y_j$  are the "**in**" and "**share**" variables (i.e. all variables whose value may be changed by the environment), and where  $y_{j+1}, ..., y_k$  are the remaining interface variables (the "**out**" variables that the environment does not change). We often refer to the module by  $m(y_1, ..., y_j; y_{j+1}, ..., y_k)$ , where the semicolon separates the **out** variables from those that the environment can read and modify (the **in** and **share** variables).

**Definition 5:** Two modules  $m_1$  and  $m_2$  are *interface compatible*, provided each variable  $v \in is(m_1) \cap is(m_2)$  satisfies the following constraints: the types declared for v in both interfaces match, the conjunction of their **where** clauses (supposed *true* when not specified) is satisfiable, and if one of the declarations specifies an **out** mode, then the other specifies an **in** mode.

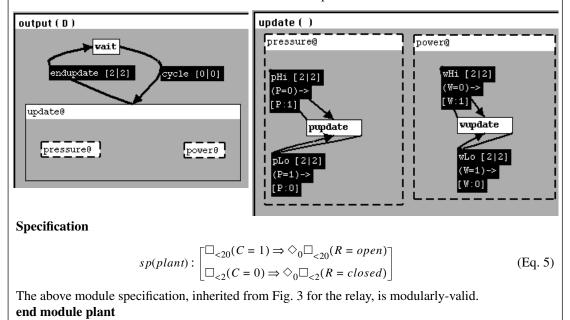

The reactor trip relay module *relay* (taken from the example in Sect. 5.2) is shown in Fig. 3. When the command to open the relay (C = 1) comes from the environment, then the relay is immediately opened (R = open) before the next clock tick, thus shutting down the reactor. The specification of the relay (see (Eq. 6) in Fig. 3) does not contain the next operator  $\bigcirc$  in the consequent; instead, the operator  $\diamondsuit_0$  is used. This is because the trajectories of a module may have environmental steps that leave the state unchanged. Specifications must therefore allow such "stuttering" steps otherwise the specification will not be modularly-valid.

#### module relay(C;R)

**in** *C*: {0,1} **where** initially (*C* = 0)

/\* when the input command (C = 1) is given, the relay is opened, and when (C = 0) the relay is closed \*/ out *R*: {open, closed} where initially (R = closed)

/\* R is the relay object variable that is exported as readonly output \*/

#### Body TTMchart (using the StateTime Build tool)

S

Note: The transitions trip[0,0] and closerelay[0,0] are immediate transitions, i.e. their time bounds force them to occur before the next clock tick once they become enabled. The guard of the trip transition is (C=1) and its enabling condition is (C=1,R=closed). In Build expressions, the comma is used for conjunction and the semicolon for disjunction. The update function *nil* in the *trip* transition indicates that no *data variable* (e.g. *C*) is changed; however, when the *trip* transition is taken the relay *R* is changed to *open*. This module has no private variables.

**Specification:**

$$p(relay): \begin{bmatrix} \Box_{<20}(C=1) \Rightarrow \diamondsuit_0 \Box_{<20}(R=open) \\ \Box_{<2}(C=0) \Rightarrow \diamondsuit_0 \Box_{<2}(R=closed) \end{bmatrix}$$

(Eq. 6)

/\* **Informal description:** The operator  $\diamond_0$  is needed in the consequent. Although the relay responds to a stimulus (i.e. a change in *C*) before the next clock tick, the reponse is not immediate but may occur a few states later (as actions of the environment are interleaved with actions of the relay). The above specification is modularly-valid \*/ end module relay.

### 3.3 A small example of compositional reasoning

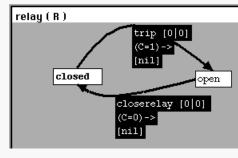

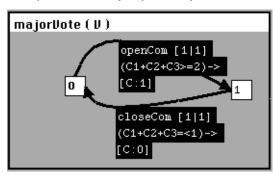

The module  $majorVote(C_1, C_2, C_3; C)$  (Fig. 4) is part of the DRT controller which will be discussed in the sequel. The controller consists of three independent microprocessors, each one with independent sensors of reactor power and pressure. Each microprocessor controller  $micro_i$  signals through a variable  $C_i$  whether to open the relay (which shuts down the reactor), or to close the relay (allowing the reactor to be started up again). The **in** variables of *majorVote* are thus  $C_1, C_2, C_3$ , and the **out** variable is C, which is set to 1 when the majority of the microprocessor vote for opening the relay (i.e. when  $C_1 + C_2 + C_3 \ge 2$ ). The specification sp(majorVote) can be shown to be modularly-valid by model-checking.

The relay module (Fig. 3) and the voting module (Fig. 4) are interface compatible. We may therefore use the modularly-valid module specifications (Eq. 6) and (Eq. 7), and the Composition Rule to prove the validity of

$$[majorVote \parallel relay] \vDash p \tag{Eq. 8}$$

where *p* is defined by:

$$p: \begin{bmatrix} [\Box_{<20}(C_1 + C_2 + C_3 \ge 2) \Rightarrow \diamondsuit_{\le 1} \Box_{<20}(R = open)] \\ \land [\Box_{<2}(C_1 + C_2 + C_3 \le 1) \Rightarrow \diamondsuit_{\le 1} (R = closed)] \end{bmatrix}$$

(Eq. 9)

The proof of the first conjunct of (Eq. 9) is as follows:

#### FIGURE 4. Module for majority voting logic

#### module majorVote(C1,C2,C3;C)

with bitType={0,1}

in  $C_1, C_2, C_3$ : bitType; /\* 1 stands for a vote to open the relay, and 0 to close the relay. \*/ out C: bitType where initially (C = 0) /\* Only *majorVote* can write to C to set the relay\*/

#### Body

**private** V: bitType where initially (V = 0) /\* majority vote object variable\*/.

Specification

$$sp(majorVote): \begin{bmatrix} \Box_{<20}(C_1 + C_2 + C_3 \ge 2) \Rightarrow \diamondsuit_{\le 1} \Box_{<20}(C = 1) \\ \land \Box_{<2}(C_1 + C_2 + C_3 \le 1) \Rightarrow \diamondsuit_{\le 1} \Box_{<2}(C = 0) \end{bmatrix}$$

(EQ 7)

#### /\*Informal description

The first line of the specification states that once the majority of microprocessor controllers vote to open the relay, and this vote remains in place for time 20 ticks, then within one tick of the clock, the output variable C will be set so as to command the relay to open, and will remain set for 20 ticks of the clock. The second line states a similar specification for the command to close the relay. \*/

#### end module majorVote

- 1.  $\Box_{<20}(C_1 + C_2 + C_3 \ge 2) \Rightarrow \diamondsuit_{\le 1} \Box_{<20}(C = 1)$ by modular-validity of (Eq. 7)2.  $\Box_{<20}(C = 1) \Rightarrow \diamondsuit_0 \Box_{<20}(R = open)$ by modular-validity of (Eq. 6)

- 3.  $\diamond_{\leq 1} \Box_{<20}(C=1) \Rightarrow \diamond_{\leq 1} \diamond_0 \Box_{<20}(R=open)$  (2) and RTTL

- 4.  $\diamondsuit_{1} \square_{<20}(C=1) \Rightarrow \diamondsuit_{1} \square_{<20}(R=open)$

- 5.  $majorVote \parallel relay \models \Box_{<20}(C_1 + C_2 + C_3 \ge 2) \Rightarrow \diamondsuit_{\le 1} \Box_{<20}(R = open)$  (1), (4) and Composition Rule

The temporal logic reasoning is performed in the RTTL proof system. For example, the RTTL theorem used in step (3) is:  $(p \Rightarrow q) \rightarrow (\diamondsuit_{\leq 1} p \Rightarrow \diamondsuit_{\leq 1} q)$ .

The Composition Rule provides a powerful technique for beating combinatorial explosion of states. To verify a global requirement r of a system composed of modules, it is not necessary to deal with the complete system (e.g. by generating its global reachability graph). Instead, we need only verify the specification of each of its objects one at a time, provided we can show that the object specifications entail the global requirement.

The modular-validity of module specifications for a module m can be determined by applying the model-checking and theorem proving tools of StateTime (Sect. 2.4) to the TTM  $\hat{m}$  that corresponds to m. For example, the relay module specification sp(relay) in Fig. 3 can be proved modularly-valid by model-checking the set of transitions associated

(3) and RTTL

with the body together with the nondeterministic environmental transition with update function choose(C), which allows the input variable *C* to vary arbitrarily.

In the above relay example, an unrestricted environment was used to check the modular-validity of the module specification. This is not always possible as an unrestricted environment can sometimes generate larger intermediate reachability graphs than the reachability graph obtained when the environment is limited to a known set of fixed modules. This is because certain states of the module in an unrestricted environment may be unreachable in the composite. There are two ways to address this issue: either (a) decompose the module into smaller sub-modules where an unrestricted environment will not be problematic, or (b) restrict the environment of the module to the actual environment in which the module is expected to operate.

The easiest way to restrict the environment involves the use of *conditional specifications* for the module of the form  $Env \rightarrow r$  which asserts that if the environment is assumed to behave according to the RTTL formula Env then the module is guaranteed to behave according to the RTTL formula r. In other frameworks, such conditional specifications are called assumption/guarantee properties [22], and special rules are provided for reasoning about them. In our framework, conditional specifications are no different from any other module specifications. Our purpose will be to show that  $Env \rightarrow r$  is modularly-valid for the module m, i.e.  $m \models Env \rightarrow r$ . This does not contradict our definition that a module specification should hold independently of what the environment does. The property rwill indeed hold true only if the module environment; this is because if the environment does not satisfy Env, then r need not hold true [32, p.356].

In the sequel, we deal with modules that are intended to work in fixed environments. For example, the environment of the DRT *controller* module (Sect. 5.0) is the *plant* which will remain fixed throughout the design. Consider a conditional specification  $des(plant) \rightarrow r$  for one of the controller sub-modules m which asserts that if the plant (which is the environment of m) behaves according to des(plant) then m will behave according to r. To verify the modular-validity  $m \models des(plant) \rightarrow r$  in an unrestricted environment in which the plant output variables can take on any value at any moment, will generate a larger reachability graph than necessary because there will be states that are not reachable in practice. The actual plant sensors are filtered and hence change only every two ticks of the clock. Thus we do not need to consider all the possibilities generated by continuously changing sensor values. Instead, we can verify  $[plant || m] \models r$  which will involve a smaller reachability graph in which plant changes occur only every two ticks. The following theorem justifies this procedure.

**Theorem 3:** Let  $m_1$  and  $m_2$  be two compatible modules and p an RTTL formula in the interface variables. Then  $[m_1 \models des(m_2) \rightarrow p] \equiv [m_1 \parallel m_2] \models p$ .

#### **Proof:**

$[m_1 \vDash des(m_2) \rightarrow p]$   $\equiv \langle (\text{Th. 1})(a) \rangle$   $\vDash des(m_1) \rightarrow [des(m_2) \rightarrow p]$   $\equiv \langle \text{propositional temporal logic} \rangle$  $\vDash des(m_1) \land des(m_2) \rightarrow p$  ≡ < Composition Rule and  $m_i \models des(m_i)$  holds for i = 1, 2 by (Th. 1)(b) >  $[m_1 \parallel m_2] \models p$ . ■

# 4.0 Module refinement

If a module m has been implemented with a given body, under what conditions can we replace the body with a new one while still retaining the same observed timed behaviour at the interface stub? One possibility is to use the notion of program equivalence of untimed concurrent programs developed in [32, p46]. However, this notion of equivalence will not work for our real-time reactive modules.

Consider a program with two variables x and y. In [32, p46], a sub-sequence  $\langle \varepsilon:start, x:0, y:0 \rangle \langle \varepsilon:tick, x:0, y:0 \rangle \langle \varepsilon:tick, x:0, y:0 \rangle \langle \varepsilon:\tau, x:1, y:2 \rangle$  is reduced to  $\langle \varepsilon:start, y:0 \rangle \langle \varepsilon:tick, y:0 \rangle \langle \varepsilon:\tau, y:2 \rangle$  if we want to observe variable y. We have thus lost a record of one of the clock ticks, because in the refinement relation of [32], program states that are identical to their predecessors are omitted from the sequence. But, in real time systems, it is essential that the reduced system show the same *timed* behaviour as the original system. We will thus need to define a notion of observational equivalence that takes into account state (data such as the value of y) as well as events (ticks of the clock). In this section, we adapt the *state-event* notion of *observational equivalence* developed in [26,27,28] to the needs of real-time reactive modules. Because we need to deal with both states and events, we also cannot just use the standard event-based notion of bisimulation [33], as will be explained in this section.

Consider two modules that have the same interface stub but different bodies. For such modules we will define a notion of module observational equivalence that is *compositionally consistent* and preserves *any* stuttering invariant RTTL module specification (detailed explanation follows below). Thus the first body can be replaced by the second with a guarantee that any module specification that holds for the first will also hold for the second, and vice versa. Observational equivalence will allow us to *refine* an abstract module into one closer to code implementation. The abstract module may have a substantially smaller state space than the refinement and hence will be more amenable to model-checking.

Informally, if a module  $m_1$  is equivalent to a module  $m_2$  having the same interface stub (written  $m_1 \approx m_2$ ) then  $m_1$  preserves the timed behavior of  $m_2$  over the interface variables. We want a notion of observational equivalence that only distinguishes between the two modules if the distinction can be detected by an external agent interacting with each of them. The agent can observe any of the interface variables and the *start* transition and *tick* of the conceptual global clock, but not any of the private variables or internal transitions which are unobservable to the external agent. We call such internal unobservable actions  $\lambda$ -transitions. Although an external agent may not be able to observe an internal transition itself, it may be able to observe the effects of the internal transition (e.g. if the internal transition changes one of the interface variables).

### 4.1 Observation equivalence of TTMs

In [37], an algorithm is given for constructing the reachability graph of a TTM. The reachability graph is used as the basis for model-checking RTTL formulas, as maximal fair paths in the reachability graph correspond to TTM trajectories.

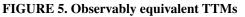

We illustrate the concept of a reachability graph by referring the reader to the sample TTM  $N_1$  with variables set  $V = \{\varepsilon, c, v\}$  as shown in Fig. 5. The reachability graph of  $N_1$   $rg(N_1) = (Q, T, R, q_1)$  is also shown in Fig. 5. The reachability graph is a labelled transition system with state set Q, transition label set  $T = \{start, tick, a, b\}$ , R is a set  $\{R_{\tau} | \tau \in T\}$  of binary relations on Q, and the initial state is  $q_1 = \langle c:on, v:0 \rangle$ .

If  $q, q' \in Q$  and  $\tau \in T$  then  $R_{\tau}(q, q')$  holds precisely when  $s' \in \tau(s)$  (i.e. s' is a  $\tau$ -successor of s) where q, q' are the restrictions of s, s' respectively, and s, s' both occur in trajectories of the TTM  $N_1$ . Let  $\tau(q, q')$  be an abbreviation for  $R_{\tau}(q, q')$  which is called a  $\tau$ -step from q to q'. The notation  $tick(q_1, q_2)a(q_2, q_3)tick(q_3, q_4)...$  denotes a sequence of steps in the graph. Any maximal sequence of steps in the reachability graph corresponds to a trajectory of the TTM respecting the initialization, succession, fairness, and bound constraints (Sect. 2.2).